Разделы сайта

- Главная

- Электроника: интересно и познавательно

- Организация производства радиоэлектронной техники

- Телефонные переговоры по технологии IP-телефонии

- Информационно-компьютерная система службы видеонаблюдения

- Физические основы электроники

- Автоматические системы управления

- Цифровые устройства и приемники

Выбор элементной базы

Для проектирования блока ОЗУ были рассмотрены особенности функционирования процессора 8080. Было выяснено что его максимальная частота функционирования составляет 2.5МГц и разрядность шины данных - 8 бит, шины адреса - 16 бит. Анализируя временные диаграммы рассчитываем, что каждый следующий такт выполняется через 0.4 мкс, учитывая что каждый такт состоит из двух полутактов то для работы в синхронном режиме требует памяти с задержкой не более 0.2мс. Исходя из всего перечисленного для работы процессора без тактов ожидания решено использовать статическую память имеющую минимальные задержки.

С шины управления для правильного функционирования ОЗУ необходимо контролировать следующие сигналы:- запись на этом выходе МП БИС сигнал указывает, что данные выданы МП БИС и установлены на МД (магистраль данных) и могут быть записаны в ОЗУ. Этот сигнал необходим для выбора направления передачи данных.- чтение внешнего порта , используемый для выбора вместо ОЗУ адресного пространства портов.- запись внешнего порта , используемый для выбора вместо ОЗУ адресного пространства портов.

Два последних сигнала в активном 1ом состоянии сигнализируют о том что блок ОЗУ должен быть отключен от шины данных, а буфер переведен в Z состояние.

Для выполнения выбора конкретной микросхемы также следует учесть что можно выбрать ОЗУ только из ряда 4кб,8кб,16кб, 32кб и т.д. в связи с этим есть два варианта реализации: взять ОЗУ 16кб х 8 или две микросхемы на 8 +4 кб. Первый вариант по моему мнению предпочтительнее однако часть ОЗУ останется неиспользованной поэтому было решено реализовывать второй вариант. Для выбора микросхемы был проведен поиск в интернете и доступной мне литературе. В учебнике Г.И. Пухальский «Проектирование микропроцессорных систем» были рассмотрены как российские аналоги серия 537РУхх так и импортные варианты ОЗУ , при этом была найдена подходящая по параметрам микросхема. Учитывая что задержки для большинства микросхем 537 серии близки к 0.2 мкс что обеспечивает требуемые параметры задержек первая микросхема была взята 537РУ16 обеспечивающая 8Кбайт на 8бит, задержка при выборке 140/160нс.

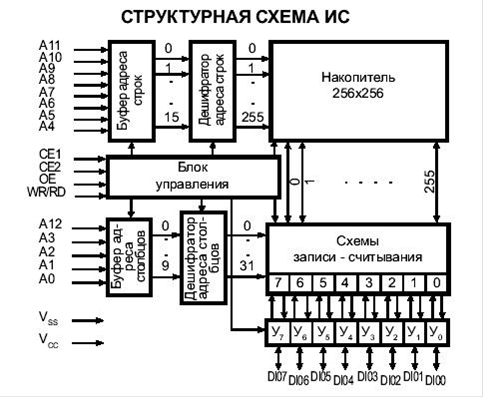

Рис.2. Структурная сема микросхемы ОЗУ 537РУ16.

На схеме видна внутренняя структурная схема и организация данной микросхемы. Использование тригерных ячеек памяти значительно повышает скорость работы такого ОЗУ по сравнению с динамическим которое реализуется на конденсаторах.

Далее был произведен поиск микросхемы 4кбайта на 8бит, была найдена микросхема статического ОЗУ CY7С138. Данная микросхема статического ОЗУ имеет двухпортовую организацию и имеет расширенные возможности, а также высокую скорость выборки данных не более 120нс. Обе микросхемы построены на CMOS технологии но совместимы с логикой ТТЛ питание микросхем осуществляется от 5В.

Проанализировав требуемые для реализации функции были выбраны следующие микросхемы логики:

К555ЛП5,чип имеет четыре стандартных элемента исключающее ИЛИ.

Стандартные серии ТТЛ: 533, 555.

Время задержки 10 нс,

мощность потребления 55 мВт

Интересное из раздела

Ошибки позиционирования GPS-приемников в условиях полярных геомагнитных возмущений

Определение своего положения с помощью GPS навигатора,

отдельного прибора, или устройства, встроенного в карманный компьютер или

сотовый тел ...

Внедрение технологии спектрального уплотнения на участке ст. Свердловск – ст. Тюмень

В последние два десятилетия прошедшего и в начале текущего века

происходит смена эпохи индустриально-технологического развития передовых

государств эпохой и ...

20-разрядный аналого-цифровой преобразователь, изготовленный по технологии КМОП 0,9 пм

Традиционные

конструкции аналого-цифровых преобразователей (АЦП) использовали параллельную

архитектуру и биполярные технологии для получения 8-битного разрешени ...