Разделы сайта

- Главная

- Электроника: интересно и познавательно

- Организация производства радиоэлектронной техники

- Телефонные переговоры по технологии IP-телефонии

- Информационно-компьютерная система службы видеонаблюдения

- Физические основы электроники

- Автоматические системы управления

- Цифровые устройства и приемники

Определение требований к быстродействию триггеров и логических элементов

При выполнении данного пункта необходимо принять следующее допущение:

tt

-задержки во всех логических элементах считаются равными, и равняются t.

Согласно исходным данным наибольшая частота входных (тактовых) импульсов Fmax = 5 МГц

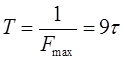

Период определяем, как

![]()

Или имеем:

![]() ,

,

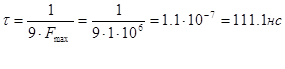

где ![]() - время импульса, которое мы определяем как:

- время импульса, которое мы определяем как:

![]() , где

, где ![]() - время на срабатывание первой ступени триггера.

- время на срабатывание первой ступени триггера.

Определяем ![]() , которое состоит из времени задержки JK -триггера

, которое состоит из времени задержки JK -триггера ![]() и длительности сигнала управление

и длительности сигнала управление ![]() .

.

Определяем длительность паузы.

![]()

Определяем время на срабатывание второй ступени триггера ![]() , которое состоит из времени срабатывания ступени

, которое состоит из времени срабатывания ступени ![]() дополненной длительностью

дополненной длительностью ![]() на срабатывание инвертора.

на срабатывание инвертора.

Определяем ![]() исходя из самой длинной цепи, которая включает 2 элемента. Следовательно получаем:

исходя из самой длинной цепи, которая включает 2 элемента. Следовательно получаем: ![]()

Имеем:

![]()

![]()

Следует:

Вывод

ы

В ходе выполнения курсовой работы был спроектирован счётчик-делитель параллельного типа с модулем счёта 13 с использованием JK-триггеров на основе логического базиса И-НЕ. Было рассчитано требование к быстродействию триггеров и логических элементов. Схема была исследована на ПЭВМ. Результаты исследования были представлены в отчёте и совпали с теоретическими.

Также были получены практические навыки по разработке функциональных схем цифровых узлов на основе метода минимизации булевых функций и методов синтеза цифровых узлов в заданном базисе, закреплен опыт применения ПЭВМ для контроля правильности расчетов и исследования спроектированного функционального узла.

Интересное из раздела

Линейная антенная решетка

Антенны СВЧ широко применяют в различных областях

радиоэлектроники - связи, телевидении, радиолокации, радиоуправлении, а также в

системах инструмент ...

Проект макета на основе PIC контроллера

Сегодняшний день развития вычислительной техники характеризуется бурным

развитием сетевых технологий. При этом, основной упор делается на технологии,

позволяющи ...

Беспроводные локальные сети Wlan (wi-fi)

Так

сложилось, что в нашей стране большую распространенность получили районные

Ethernet сети, затягивающие в квартиру витую пару. Когда дома всего один

ком ...