Разделы сайта

- Главная

- Электроника: интересно и познавательно

- Организация производства радиоэлектронной техники

- Телефонные переговоры по технологии IP-телефонии

- Информационно-компьютерная система службы видеонаблюдения

- Физические основы электроники

- Автоматические системы управления

- Цифровые устройства и приемники

Описание схемы

Так как цифровые входы X-Z управляют только двумя конденсаторами, этот ЦАП создает только три уровня. Игнорируя паразитные явления, коэффициент обратной связи здесь С1/С1+Сs или ½ когда С1 = Сs. При тех же условиях, коэффициент обратной связи в стандартном умножающем ЦАП с разрешением 2-b (с двумя дополнительными конденсаторами выборки) равен С1/(С1+2Сs) или 1/3. Если умножающий ЦАП с тремя уровнями и разрешением 2-b использует тот же операционный усилитель, то различие в коэффициентах обратной связи преобразуются в различия в цикле усиления; поэтому, игнорируя паразитные влияния, трёхуровневый умножающий ЦАП на 50% быстрее, чем стандартный дубликат с разрешением 2-b. Это важно, потому что скорость умножающего ЦАП ограничивает скорость преобразования АЦП. Многие архитектуры операционных усилителей могут получить коэффициент усиления при разомкнутой цепи, по крайней мере, 2000; однако, немногие из них способны получить время урегулирования менее чем 25 нс в технологии 1-pm CMOS. Предыдущие проекты быстрых операционных усилителей на переключаемых конденсаторах имеют класс A/B и архитектуру свернутого каскада [9], [22]. Чтобы минимизировать сигнально-зависимый текущий источник питания и чтобы избавится от необходимости использовать p-канальные транзисторы на пути сигнала, здесь используется операционный усилитель развернутого каскада класса А.

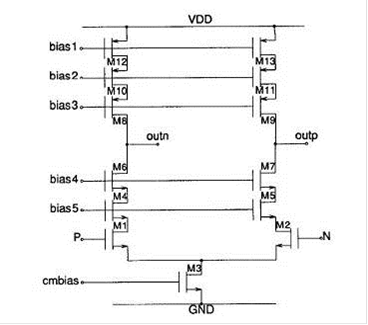

Рисунок 8 - Схема операционного усилителя

Рис. 8 показывает схему операционного усилителя. Она состоит из входной дифференциальной пары (М1, М2), источника тока (М3), двух уровней n-канальных каскадов (М4-М7), двойных p-канальных каскадов (М8-М13) в качестве нагрузки. Обратная связь общего режима переключаемых конденсаторов и цепь смещения используются также, но не показаны для упрощения схемы. Согласно моделированию, усиление операционного усилителя составляет около 80 дБ и его выход урегулируется в течение 20 нс с 4-V дифференциальным выводом в нагрузку на 3 пФ. Эта схема отлична от той, что показана на [18], в которой только использовался один уровень каскадов n-типа. Дополнительный уровень из каскадов здесь был вставлен для увеличения усиление разомкнутого цикла операционного усилителя, чтобы уменьшить нелинейность АЦП [18].

АЦП низкого разрешения состоит из линейки резисторов, банка компараторов и кодера и сконструирован, так же как и в [9], за исключением того, что здесь на этап требуется только два компаратора.

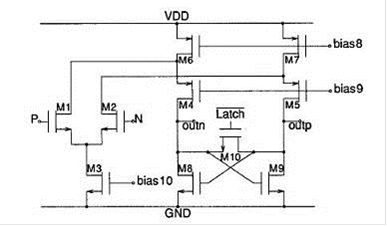

Рисунок 9 - Схема компаратора

На рис. 9 показана схема компаратора. Схема состоит из свернутого каскадного усилителя (М1-М7) в котором нагрузка заменена защелкой (М8-М10). А архитектура свернутого каскада выбрана так, что n-канальные транзисторы могут использоваться и в дифференциальной паре и в защелке. Когда М10 открыт, выходы компаратора соединены вместе и к затворам М8 и М9. В этой конфигурации ток, вытекающий из каскада, течет через М10. Когда М10 закрыт, выводы компаратора разделены, оставляя М8 и М9 подключенными в конфигурации положительной обратной связи. В результате дифференциальные потоки, выходящие из каскадов заряжают выходной паразитный узел и вывод фиксируется; т.е. один выход уходит к положительному питанию, а другой - в землю. Поскольку защелка активирована, активная нагрузка не требуется. Это уменьшает выходную паразитную емкость и в результате ускоряет компаратор. Согласно моделированию, компаратор требует около 8 нс для установки.

Экспериментальные результаты.

На Рис. 10 показана линейность постоянного тока АЦП со скоростью преобразования 20 Msamples/s. На Рис. 10(а) дифференциальная нелинейность изображена графически, а на Рис. 10(b) изображена интегральная нелинейность. Величины максимального значения DNL и INL менее чем 0.2 и 0.25 от LSB соответственно. Нелинейность здесь приблизительно в 4 раза меньше чем показанная на [18]. Это улучшение вызвано увеличением коэффициента усиления операционного усилителя при разомкнутой цепи описанное в 4 разделе и влияет на производительность так хорошо, как показано далее. Рис. 11 показывает выход быстрого преобразования Фурье на блоке 4096 последовательных кодов. Скорость преобразования 20 Msamples/s и вход - полномасштабная синусоида с частотой 4.97 МГц. SNR около 60 дБ; SDR около 74 дБ; SNDR примерно 60 дБ. SDR примерно на 14 дБ больше, чем на рисунке [18]. Потому что SNR ограничено шумом квантования, однако, SNDR здесь также ограничено шумом квантования. Далее, выводы БПФ, такие как на Рис. 11, использовались, чтобы создавать графики зависимости SNDR от входящего уровня, частоты и скорости преобразования. Рис. 12 показывает графики зависимости SNDR от входящего уровня для двух входных частот: 100 КГц и 19.9 МГц. Вход с частотой 19.9 МГц моделируется со скоростью 20 Msamples/s в 100 КГц выход АЦП. Идеальна кривая 10-b также показана. Обе кривые близки к идеалу, кроме мест высокого входного уровня сигнала. Для входа 100 КГц пиковый уровень SNDR примерно 60 дБ вместо 62 дБ для идеального случая. Для входа 19.9 МГц пиковый уровень SNDR примерно 55 дБ. Эти различия вызваны искажениями, полученными от входов SHA.

Интересное из раздела

Цифровой показатель уровня топлива

Топливомер - прибор, измеряющий объемное или весовое количество топлива или масла в баках. Как правило, непосредственное измерение количества топлива крайне затруднено, п ...

Программируемый генератор сигналов

Современное состояние и перспективы развития многих отраслей техники, в

том числе и радиоэлектроники, во многом определяются широким проникновением

средств ...

Автоматизация судовой энергетической установки

Автоматическое управление технологическими процессами является одним из главных направлений научно-технического прогресса на морском транспорте.

Автоматизация СЭУ обеспе ...