Разделы сайта

- Главная

- Электроника: интересно и познавательно

- Организация производства радиоэлектронной техники

- Телефонные переговоры по технологии IP-телефонии

- Информационно-компьютерная система службы видеонаблюдения

- Физические основы электроники

- Автоматические системы управления

- Цифровые устройства и приемники

Модуль микропроцессора

- Программирование через JTAG интерфейс: Flash, EEPROM памяти, перемычек и битов блокировки.

- Встроенная периферия:

- Два 8-разрядных таймера / счетчика с отдельным предварительным делителем, один с режимом сравнения.

- Один 16-разрядный таймер / счетчик с отдельным предварительным делителем и режимами захвата и сравнения.

- Счетчик реального времени с отдельным генератором.

- Четыре канала PWM.

- 8-канальный 10-разрядный аналого-цифровой преобразователь.

- 8 несимметричных каналов.

- 7 дифференциальных каналов (только в корпусе TQFP).

- 2 дифференциальных канала с программируемым усилением в 1, 10 или 200 крат (только в корпусе TQFP).

- Байт-ориентированный 2-проводный последовательный интерфейс.

- Программируемый последовательный USART.

- Последовательный интерфейс SPI (ведущий / ведомый).

- Программируемый сторожевой таймер с отдельным встроенным генератором.

- Встроенный аналоговый компаратор.

- Специальные микроконтроллерные функции:

- Встроенный калиброванный RC-генератор.

- Внутренние и внешние источники прерываний.

- Шесть режимов пониженного потребления: Idle, Power-save, Power-down, Standby, Extended Stand by и снижения шумовADC.

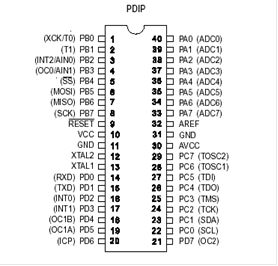

- Выводы I/O и корпуса

- 32 программируемые линии ввода / вывода

- 40-выводной корпус PDIP и 44-выводной корпус TQFP

- Рабочие напряжения 4,5 - 5,5 В

- Рабочая частота 0 - 16 МГц

Рисунок 3.3 - Выводы микроконтроллера

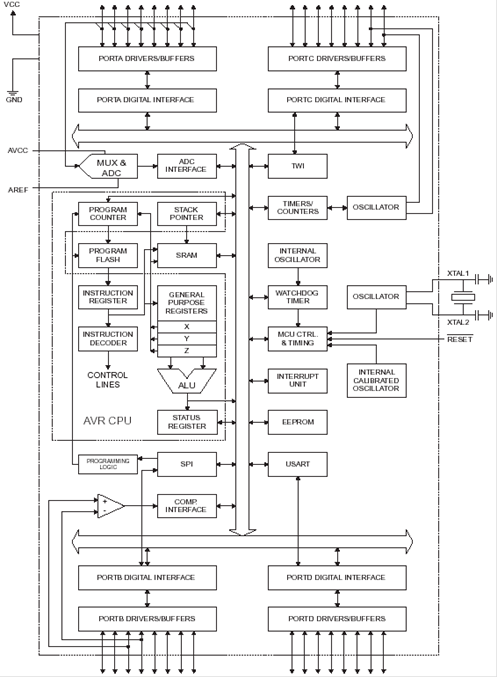

ATmega16 - низкий-силовой бит CMOS 8-microcontroller основанный на AVR расширившее архитектуру RISC. Выполняя мощные инструкции в единственном цикле часов, ATmega16 достигает производительности, достигающей 1 MIPS за МГЦ, допускающий системного разработчика, чтобы оптимизировать силовое потребление против обработки скорости.

Сердцевина AVR объединяет богатую инструкцию установленную 32 универсальными работами регистров.

Все 32 регистра непосредственно подключены к Арифметическому Логическому Устройству (ALU), допуская два независимых регистра, чтобы быть доступно в одной единственной инструкции выполненной в одном цикле часов.

Результирующая архитектура более кодовая эффективная достигая производительности вплоть до десяти раз быстрее чем стандартных microcontrollers CISC.

ATmega16 обеспечивает следующее характеристик: байты 16K, программируют память с возможностями Read-While-Write, 512 байтов EEPROM, байт 1K SRAM, 32 универсальных строки В/В, 32 универсальных работы регистров, интерфейс JTAG для Границы-сканирования, В-чипе, отлаживающем поддержку и программирование, три гибких Timer/Counters с режимами сравнения, внутренних и внешних прерываний, последовательным программируемым USART, байт ориентировал на двухпроводной последовательный интерфейс, программируемым таймером с внутренним генератором, последовательный порт SPI, и шесть программных избирательных мощностей, сохраняющих режимы.

Режим Ожидания останавливает CPU допуская USART, Двухпроводной интерфейс, A/D Преобразователя, SRAM, Timer/Counters, порт SPI, и система прерывания, чтобы продолжать функционировать.

Силовой-пониженный режим сохраняет содержание регистра, но замораживает генератора, блокируя все другие миниатюрные функции пока следующее внешнее прерывание или аппаратные средства не восстановлены.

Рисунок 3.4 - Блок - схема ATmega16

В силовом-сохраняемом режиме, асинхронный таймер остается работать, допускающий пользователь, чтобы поддерживать таймерную базу тогда как остальная часть устройства спит.

Режим Уменьшения Шума ADC останавливает CPU и все модули В/В кроме Асинхронного Таймера и ADC, чтобы минимизировать переключение шума в течение преобразований ADC.

Интересное из раздела

Определение параметров нелинейности усилителя аппаратуры ВЧ связи по ЛЭП на основе аппроксимации его коэффициента усиления и выбор оптимального режима

1. Аппроксимировать

полиномом седьмой степени экспериментальную зависимость коэффициента усиления

Кэ = f ( Uсм

) заданного усилительного каскада н ...

Взаимодействие сигналов контроля в сети NGSDH с трактами VC-12

Телекоммуникации всегда были одной из бурно развивающихся

отраслей. С момента зарождения и до нашего времени, сети электросвязи прошли

через целый ряд революц ...

Беспроводные локальные сети Wlan (wi-fi)

Так

сложилось, что в нашей стране большую распространенность получили районные

Ethernet сети, затягивающие в квартиру витую пару. Когда дома всего один

ком ...