Разделы сайта

- Главная

- Электроника: интересно и познавательно

- Организация производства радиоэлектронной техники

- Телефонные переговоры по технологии IP-телефонии

- Информационно-компьютерная система службы видеонаблюдения

- Физические основы электроники

- Автоматические системы управления

- Цифровые устройства и приемники

Проведенные моделирования

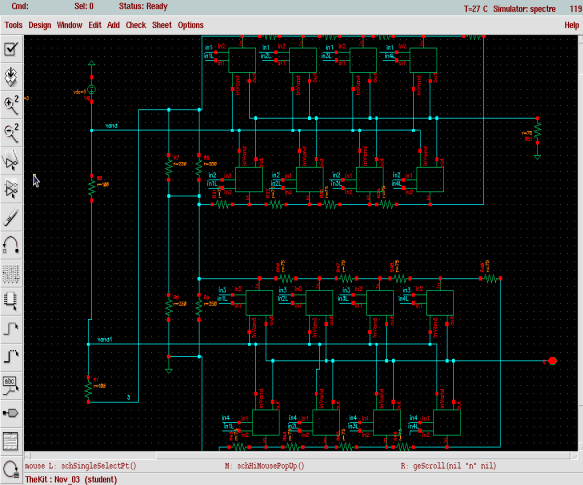

Для сокращения времени моделирования сделаем ЦАП четырёхразрядным. Таким образом, получим структуру с 16ю основными ячейками, четырьмя резисторами в грубой лестнице, и двумя в лестнице питания. Входящее четырёхразрядное слово будет разбиваться на 2 двухразрядных, который будут декодироваться четырьмя декодерами MSB и четырьмя декодерами LSB. Резисторная сеть представлена на Рисунке 3.

Рис.3 - Резисторная сеть

Лестница питания понижает напряжение с Vdd (которое у нас равно 3В) до 1.5В, которое уже подаётся на основную лестницу. Номиналы этих 2х резисторов будут по 100 Ом. Резисторы грубой лестницы будут иметь номиналы по 250 Ом. А резисторы точной (основной) лестницы - 75 Ом.

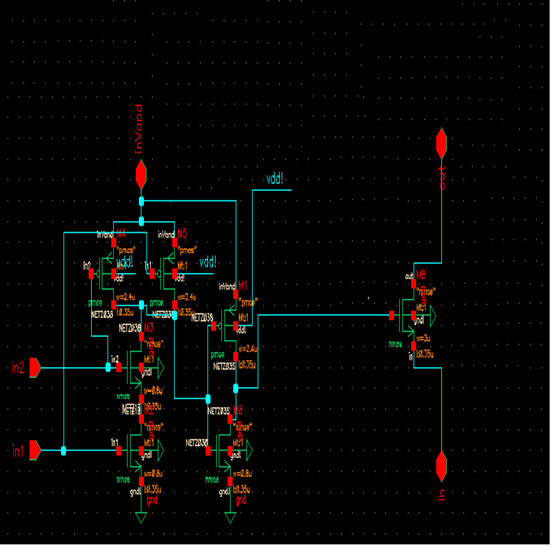

Рис.4 - Структура основной ячейки

Основная ячейка состоит из элемента «и», который получает питание от лестницы питания, и н - канального транзистора. На входы «и» подаётся сигнал от MSB и LSB декодеров. Н - канальный транзистор будет замыкаться на общую шину.

Когда включается ячейка, на шине устанавливается потенциал этой ячейки, таким образом, на одной шине возможны 8 уровней квантования, а на 2х - 16.

телевизионный стандарт видео сигнал

Интересное из раздела

Определение структуры системы обнаружения объекта охраны

В

настоящее время все больше людей приходит к выводу, что усилий только

государственных правоохранительных органов для решения такой проблемы, как

охрана ...

Cинтез инвертирующего усилителя

Операционные усилители в настоящее время находят широкое применение при

разработке различных аналоговых и импульсных электронных устройств. Это связано

с те ...

Модернизация сети широкополосного доступа оператора связи ООО ТомГейт

Информационные методы все шире внедряются во все сферы деятельности.

Информатизация, конвергенция компьютерных и телекоммуникационных технологий,

переход к ...