Разделы сайта

- Главная

- Электроника: интересно и познавательно

- Организация производства радиоэлектронной техники

- Телефонные переговоры по технологии IP-телефонии

- Информационно-компьютерная система службы видеонаблюдения

- Физические основы электроники

- Автоматические системы управления

- Цифровые устройства и приемники

Разработка структурно-функциональной схемы

Необходимо обеспечить взаимодействие процессора со специализированной микросхемой (микросхемами) ОЗУ в рамках адресного пространства меньше 12Кбайт. Для реализации требуется обеспечить согласование сигналов трех основных шин ША, ШУ, ШД.

Для контроля перехода за диапазон 12Кбайт требуется разработать дополнительный селектор и дешифратор адреса.

микропроцессор микросхема память

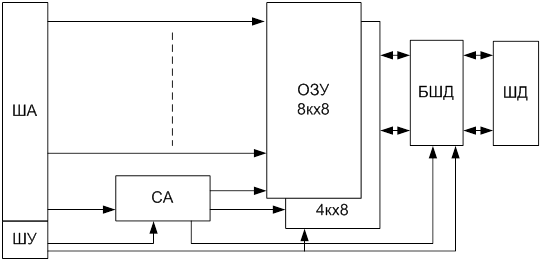

Рис. 1 Структурно-функциональная схема ОЗУ.

• ША - шина адреса

• ШД - шина данных

• ШУ - шина управления

• СА - селектор адреса

• ОЗУ - микросхемы ОЗУ

• БШД - буфер шины данных

На данной схеме поступающий адрес проходит через селектор и позволяет выбрать одну из микросхем ОЗУ одновременно, с этим управляющие сигналы указывающие, что выбрано устройство позволяют заблокировать обращение к ОЗУ даже при совпадении адресов. Еще один сигнал управления RW задает направление куда выдается информация в блок ОЗУ или на шину.

Интересное из раздела

Калибровка мониторов на основе науки о цвете – колориметрии

Полиграфическая индустрия активно развивается и предлагает

клиентам все больше новых и интересных решений. Также растет требовательность

заказчиков к резуль ...

Исследование и расчет цепей синусоидального тока

Синусоидальный ток представляет собой ток, изменяющийся во

времени по синусоидальному закону:

,

где - максимальное значение или амплитуда

...

Расчет характеристик сигналов и каналов связи

В последнее десятилетие ХХ века произошла научно-техническая революция в

области транспортной связи, в основе которой лежат два крупных достижения ...