Разделы сайта

- Главная

- Электроника: интересно и познавательно

- Организация производства радиоэлектронной техники

- Телефонные переговоры по технологии IP-телефонии

- Информационно-компьютерная система службы видеонаблюдения

- Физические основы электроники

- Автоматические системы управления

- Цифровые устройства и приемники

Прототип схемы измерения и отображения информации

· во-вторых, оставить три линии старшей тетрады порта PC для аналогово-цифрового преобразования (это верно для контроллера ATmega8; для другой модели контроллера ATmega порт назначения АЦП может быть другим). Три линии младшей тетрады этого порта зарезервировать для цифровых входов. Это можно сделать, т.к. линии портов в микроконтроллерах AVR программируются независимо.

· в-третьих, по заданию на курсовое проектирование для отображения одного измеренного сигнала необходимо использовать четырехразрядные семисегментные индикаторы, а не трёхразрядные, как это сделано в схеме на рис. 3. Кроме того, в схеме на рис. 3 нужно зарезервировать ещё три линии порта PD микроконтроллера для выбора четвёртого разряда в каждой строке, состоящей их двух четырёхразрядных индикаторов. В такой схеме восемь линий порта PA и четыре линии порта PD будут обеспечивать выбор обновляемого разряда в группе, а восемь линий порта PB и восемь линий порта PC будут служить для выбора столбца, в котором находится четырёхразрядный индикатор. Таким образом, для организации динамической индикации необходимо 28 линий микроконтроллера, что представляется нерациональным.

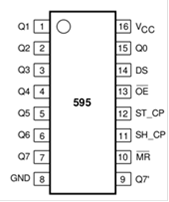

· в-четвёртых, для динамической индикации будем использовать схему с четырьмя сдвиговыми регистрами 74HC595, которая требует всего три линии микроконтроллера. 74HC595 - восьмиразрядный сдвиговый регистр с последовательным вводом, последовательным или параллельным выводом информации, с триггером-защелкой и тремя состояниями на выходе. Условное графическое обозначение (УГО) сдвигового регистра 74HC595 приведено на рис.4.

Рис. 4. УГО сдвигового регистра 74HC595.

Назначение выводов:

· ![]()

![]() выходы микросхемы. Могут находиться в трех состояниях: логическая "1", логический "0" и высокоимпедансное состояние (HI- Z);

выходы микросхемы. Могут находиться в трех состояниях: логическая "1", логический "0" и высокоимпедансное состояние (HI- Z);

· ![]()

![]() выход, предназначенный для последовательного соединения регистров;

выход, предназначенный для последовательного соединения регистров;

· ![]()

![]() вход тактовых импульсов;

вход тактовых импульсов;

· ![]()

![]() вход "защелкивающий" данные;

вход "защелкивающий" данные;

· ![]()

![]() вход данных;

вход данных;

· ![]()

![]() сброс регистра;

сброс регистра;

· ![]()

![]() вход, переводящий выходы в высокоимпедансное состояние;

вход, переводящий выходы в высокоимпедансное состояние;

· ![]()

![]() питание +5В;

питание +5В;

· ![]()

![]() земля.

земля.

Принцип работы сдвигового регистра следующий (см. [3]). При появлении логической "1" на тактовом входе SH_CP

в регистр считывается бит со входа данных DS

, который записывается в самый младший разряд регистра. При поступлении на тактовый вход следующего импульса, все повторяется, только бит записанный ранее сдвигается на один разряд, а его место занимает вновь пришедший бит. Чтобы данные появились на выходах Q0…Q7

их нужно "защелкнуть". Для этого необходимо подать логическую единицу на вход ST_CP

. Наличие триггера-защелки позволяет не беспокоиться о том, что при загрузке данных на выходе появятся ненужные промежуточные значения. Загрузили в сдвиговый регистр нужные данные, "защелкнули", и можем записывать следующие данные. И до тех пор, пока не будет подана логическая единица на вход ST_CP

, на выходах будет находиться предыдущее значение. Вход MR

осуществляет сброс регистра, устанавливая все выходы Q0 . Q7в состояние логического нуля. Для осуществления сброса необходимо подать логический "0" на этот вход, и подать тактовый импульс на вход SH_CP

Интересное из раздела

Расчет спектральных характеристик сигналов и каналов связи

На современном этапе развития перед

железнодорожным транспортом стоят задачи по увеличению пропускной и провозной

способности, грузовых и пассажирских перев ...

Анализ и синтез линейной системы автоматического управления

Анализ

системы автоматического управления

Исходные

данные:

Рассмотрим

структурную схему III

изображенную в табл. П-1.1.

Параметры

...

Автоматизация судовой энергетической установки

Автоматическое управление технологическими процессами является одним из главных направлений научно-технического прогресса на морском транспорте.

Автоматизация СЭУ обеспе ...