Разделы сайта

- Главная

- Электроника: интересно и познавательно

- Организация производства радиоэлектронной техники

- Телефонные переговоры по технологии IP-телефонии

- Информационно-компьютерная система службы видеонаблюдения

- Физические основы электроники

- Автоматические системы управления

- Цифровые устройства и приемники

20-разрядный аналого-цифровой преобразователь, изготовленный по технологии КМОП 0,9 пм

Традиционные

конструкции аналого-цифровых преобразователей (АЦП) использовали параллельную

архитектуру и биполярные технологии для получения 8-битного разрешения для

преобразования с частотой 20*![]()

![]() выборок/с. Для более чем 8-битной конструкции АЦП параллельной архитектуры

требуют больших запрещенных районов и большей потребляемой мощности. Поэтому

возник интерес к использованию многоступенчатой архитектуры. Несмотря на то,

что биполярные технологии используются для самых быстрых преобразований, для

создания многоступенчатого АЦП были так же использованы БиКМОП технологии,

которые обеспечивают достаточно высокие темпы преобразования и необходимую

частоту выборки. Стоимость таких АЦП, однако, повышается за счет более сложного

технологического процесса и требуемой рассеиваемой мощности, которая по-прежнему

достаточно высокая (по крайней мере 750 мВт). Таким образом, снижение стоимости

и мощности рассеяния с такой же или большей производительностью в технологиях

КМОП является важной задачей.

выборок/с. Для более чем 8-битной конструкции АЦП параллельной архитектуры

требуют больших запрещенных районов и большей потребляемой мощности. Поэтому

возник интерес к использованию многоступенчатой архитектуры. Несмотря на то,

что биполярные технологии используются для самых быстрых преобразований, для

создания многоступенчатого АЦП были так же использованы БиКМОП технологии,

которые обеспечивают достаточно высокие темпы преобразования и необходимую

частоту выборки. Стоимость таких АЦП, однако, повышается за счет более сложного

технологического процесса и требуемой рассеиваемой мощности, которая по-прежнему

достаточно высокая (по крайней мере 750 мВт). Таким образом, снижение стоимости

и мощности рассеяния с такой же или большей производительностью в технологиях

КМОП является важной задачей.

В

одной из предыдущих реализаций КМОП 10-битного АЦП как сообщалось, рассеиваемая

мощность была уменьшена до 250 мВт, однако, скорость его преобразования была

ограничена до 15*![]()

![]() выборок/с, а отношение сигнал/шум (SNR) 52 дБ с низкочастотным входным сигналом

и 45 дБ с частотой сигнала 7,5 МГц. В этой статье представлен девятиэтапный

конвейерный АЦП с таким же разрешением, почти такой же рассеиваемой мощностью

(240 мВт), более высокой частотой дискретизации (20*

выборок/с, а отношение сигнал/шум (SNR) 52 дБ с низкочастотным входным сигналом

и 45 дБ с частотой сигнала 7,5 МГц. В этой статье представлен девятиэтапный

конвейерный АЦП с таким же разрешением, почти такой же рассеиваемой мощностью

(240 мВт), более высокой частотой дискретизации (20*![]()

![]() выборок/с.), а так же с увеличенным отношением сигнал/шум SNR (60 дБ с входным

сигналом 5 МГц). В нем используется улучшенный алгоритм коррекции ошибок и

развернутый каскадный операционный усилитель. Преобразователь занимает 8,7

выборок/с.), а так же с увеличенным отношением сигнал/шум SNR (60 дБ с входным

сигналом 5 МГц). В нем используется улучшенный алгоритм коррекции ошибок и

развернутый каскадный операционный усилитель. Преобразователь занимает 8,7 ![]()

![]() в

технологии КМОП 0,9 пм. Кроме того, при частоте входном сигнале 5 МГц отношение

сигнал/искажения (SDR) составляет 74 дБ, отношение сигнал/шум с искажениями -

60 дБ. Основное новшество этого АЦП - улучшенный алгоритм коррекции ошибок,

который использует меньше ресурсов на одну стадию, чем в традиционной

архитектуре.

в

технологии КМОП 0,9 пм. Кроме того, при частоте входном сигнале 5 МГц отношение

сигнал/искажения (SDR) составляет 74 дБ, отношение сигнал/шум с искажениями -

60 дБ. Основное новшество этого АЦП - улучшенный алгоритм коррекции ошибок,

который использует меньше ресурсов на одну стадию, чем в традиционной

архитектуре.

Эта статья состоит из четырех основных частей. Раздел 2 представляет собой обзор конвейерных АЦП. В разделе 3 описывается новый алгоритм цифровой коррекции. В разделе 4 описаны схемы, используемые в АЦП. В конце, в разделе 5 приведены результаты экспериментов.

Обзор конвейерных АЦП

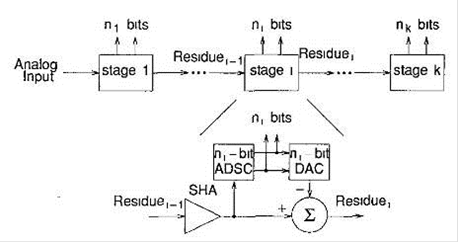

Так как основные характеристики конвейерных АЦП были подробно описаны в [7] - [11], то для удобства в этом разделе представлен только их краткий обзор. На рис. 1 представлена блок-схема конвейерного АЦП с k уровнями. Каждый уровень содержит схему выборки-хранения с усилителем (SHA), аналого-цифровой преобразователь низкого разрешения (ADSC), цифро-аналоговый преобразователь низкого разрешения (ЦАП) и вычитатель. При работе на каждый уровень поступают выборки с предыдущего уровня. Затем, входной сигнал преобразуется в цифровой код низкого разрешения с помощью ADSC и обратно в аналоговый сигнал с помощью ЦАП. В конце, сигнал на выходе ЦАП вычитается из исходного сигнала, поданного на вход, и полученный остаток поступает на следующий уровень для дальнейшего преобразования.

Рисунок 1 - Блок-схема конвейерного АЦП

Главное преимущество конвейерных АЦП в том, что они обеспечивают высокую пропускную способность и занимают небольшие области. Эти преимущества связаны с параллельной работой всех уровней, т.е. в любой момент времени первый уровень работает с новым сигналом, а все остальные уровни работают с остатком от предыдущих. (Время задержки не является ограничением в большинстве задач). Если аналого-цифровые преобразования выполняются параллельно, конвейерные архитектуры выполняют операцию за два такта, поэтому пропускная способность может быть довольно высокой. Кроме того, так как все уровни работают одновременно, их можно выбрать нужное количество для получения нужного разрешения. Таким образом, при ограничении некоторых параметров (например, общее разрешение), можно выбрать такое количество уровней, чтобы минимизировать занимаемую площадь на кристалле.

- Избыточность и цифровая коррекция

- Описание схемы

- Схема КМОП ключа

- Схема выборки-хранения

- Схема умножающего ЦАП

Интересное из раздела

Анализ и синтез линейной системы автоматического управления

Анализ

системы автоматического управления

Исходные

данные:

Рассмотрим

структурную схему III

изображенную в табл. П-1.1.

Параметры

...

Программируемый формирователь последовательности импульсов с цифровой индикацией количества импульсов

Проектируемое устройство в готовом виде представляет собой отдельный прибор, основной функцией которого является формирование последовательности импульсов заданной частот ...

Расчет линейной электрической цепи при гармоническом воздействии

Цель

курсовой работы состоит в практическом освоении методов расчета простых и

сложных электрических цепей при воздействии на них гармонических колебани ...