Разделы сайта

- Главная

- Электроника: интересно и познавательно

- Организация производства радиоэлектронной техники

- Телефонные переговоры по технологии IP-телефонии

- Информационно-компьютерная система службы видеонаблюдения

- Физические основы электроники

- Автоматические системы управления

- Цифровые устройства и приемники

Архитектура ядра

Семейство процессоров ADSP-219x - это высокопроизводительные процессоры ЦОС для коммуникаций, инструментов, управления в индустрии, обработке голоса/речи, медицине, военных применений и т.д. Эти процессоры совместимы с предшествующими процессорами ЦОС семейства ADSP-2100, но отличаются множеством дополнительных особенностей. Ядро ADSP-219x совмещено с периферией на кристалле для возможности формирования завершённых однокристальных систем (систем-на-кристалле). Внешняя для ядра (но располагающаяся на том же кристалле) периферия содержит статическую оперативную память (СОЗУ), интегрированную периферию ввода/вывода (I/0), таймер и контроллер прерываний

Архитектура ADSP-219x совмещает высокопроизводительное процессорное ядро с высокопроизводительными шинами (ПП, ПД, ПДП). Ядро исполняет любую вычислительную команду за один цикл. Для поддержания высокой скорости выполнения операций шины и КЭШ команд обеспечивают быстрый, беспрепятственный поток данных к ядру.

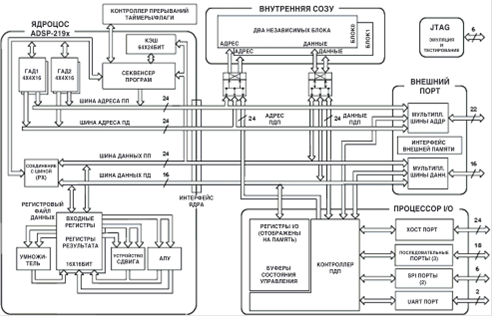

На рисунке 1 показана детальная блок-диаграмма процессора, иллюстрирующая следующие особенности архитектуры:

Вычислительные блоки - умножитель, АЛУ, устройство сдвига и регистровый файл данных.

Программный секвенсер с КЭШем команд, таймер интервалов и Генераторы Адреса Данных (ГАД1 и ГАД2).

Двухблоковая статическая оперативная память.

Внешние порты для организации интерфейса с внешней памятью, периферией и хост-процессорами.

Процессор Ввода/Вывода (I/O) со встроенными контроллерами ПДП, последовательными портами (SPORTы), порты последовательного интерфейса с периферией (SPI) и порт UART.

Порт Доступа Тестирования JTAG для тестирования и эмуляции (Порт внутрисхемного отладчика).

На рисунке 1 также показаны три шины ядра ADSP-219x: шина Памяти Программ (ПП), шина Памяти Данных (ПД) и шина Прямого Доступа к Памяти (ПДП). Шина ПП обеспечивает доступ и к инструкциям, и к данным. В течение одного цикла, эти шины предоставляют процессору доступ к двум операндам (один из ПП, и один из ПД) и одной команде (из КЭШа).

Шины соединяются с внешним портом ADSP-219x, который обеспечивает интерфейс процессора с внешней памятью, устройствами с отображением на память (I/O memory-mapped) и загрузочной памятью. Внешние порты выполняют арбитраж шины и вырабатывают сигналы управления общей памяти, глобальной памяти и устройствам ввода/вывода.

Далее показаны, современные требования к процессорам ЦОС и на сколько ADSP-219x отвечает современным требованиям:

Быстрые, гибкие арифметические вычислительные блоки

Быстрая, гибкая арифметика. Процессоры ЦОС семейства ADSP-219x выполняют все вычислительные команды за один цикл. Они обеспечивают как малый период цикла (высокая частота), так и полноценный набор арифметических операций.

Беспрепятственный поток данных к вычислительным блокам и от них

Беспрепятственный поток данных. Ядро ADSP-219x имеет модифицированную Гарвардскую архитектуру, совмещённую с регистровым файлом данных. В каждом цикле процессор ЦОС может:

Читать два значения из памяти или записать в память одно значение

Совершить одно вычисление

Записать до трёх значений обратно в регистровый файл

Увеличенная точность и динамический диапазон в вычислительных блоках

Точность, увеличенная до 40 разрядов. Процессор ЦОС оперирует с 16-ти разрядными целым и дробным форматами (попарно-комплементарные числа со знаком или числа без знака). Процессоры заносят числа с улучшенной точностью в регистры результата, уменьшая ошибки промежуточных округлений.

Сдвоенные Генераторы Адреса с возможностью организации циркулярного буфера

Сдвоенные Генераторы Адреса. В ядре есть два генератора адреса данных (ГАДы), которые обеспечивают непосредственную или косвенную (с пре- и пост-изменением) адресацию. Модульные и бит-реверсивные операции поддерживают только размещение буфера данных в пределах страницы.

Эффективная организация последовательности программ

Эффективная организация последовательности программ. В дополнение к организации циклов с нулевым количеством дополнительных тактов, ядро ЦОС поддерживает быстрые установку и выход для циклов. Циклы могут быть вложенными (восемь уровней в аппаратном обеспечении), и могут останавливаться прерываниями. Процессоры поддерживают как задержанные ответвления, так и ветви без задержки.

Интересное из раздела

Проектирование генераторного триода дециметрового диапазона

Генераторные

лампы предназначены для генерирования и усиления электрических колебаний низких

и высоких частот. По роду работы генераторные лампы можно разде ...

Проектирование железнодорожного узла связи на основе цифровой АТС Квант-Е

Цифровая система коммутации «Квант-Е» имеет модульное построение,

распределенную коммутацию, децентрализованное программное управление и

возможность централ ...

Установка акустической системы в автомобиль Honda Civic

Еще недавно желание иметь в

автомобиле аудиосистему класса НІ-FІ расценивалось большинством окружающих в

лучшем случае как бездумная трата денег. Однако для ...