Разделы сайта

- Главная

- Электроника: интересно и познавательно

- Организация производства радиоэлектронной техники

- Телефонные переговоры по технологии IP-телефонии

- Информационно-компьютерная система службы видеонаблюдения

- Физические основы электроники

- Автоматические системы управления

- Цифровые устройства и приемники

Архитектура ядра

Таймеры.

В процессоре ADSP-2191 есть три идентичных 32-разрядных таймера, каждый из которых может быть настроен независимо от других на работу в одном из следующих режимов:

Режим ШИМ (PWMOUT)

Режим Счёта и Захвата (WDTH_CAP)

Режим ожидания внешних событий - Watchdog (EXT_CLK)

У каждого таймера есть внешний вывод TMRx. Этот вывод служит выходом в режиме PWMOUT, и входом в режимах WDTH_CAP и EXT_CLK. Для обеспечения этих функций в каждом таймере имеется по семь 16-ти разрядных регистров. Для улучшения диапазона и точности шесть из этих регистров могут быть попарно объединены для получения 32-х разрядных значений.

2.2 Описание процессора ADSP-2192

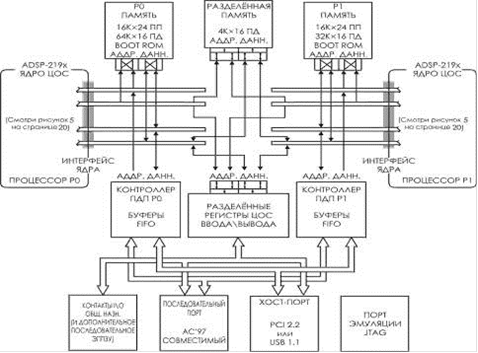

- однокристальный микрокомпьютер оптимизированный для ЦОС и для других приложений высокоскоростной обработки чисел, и он идеально вписывается в периферию персональных компьютеров. совмещает на кристалле базовую архитектуру семейства ADSP-219x с двумя процессорными ядрами ADSP-2192 (рисунок 4).включает в себя PCI-совместимый порт, USB-совместимый порт, AC’97-совместимый порт, контроллер ПДП, программируемый таймер, выводы программируемых флагов общего назначения, расширенные возможности прерываний и интегрированные пространства памяти данных и памяти программ.

В ADSP-2192m интегрировано 132К слов памяти, настроенной, как 32К 24-разрядных слов оперативной памяти программ и 100К 16 разрядных слов оперативной памяти данных (ADSP-2192m - самый маломощный из процессоров ADSP-2192); также включена схемотехника понижения потребляемой мощности

Рисунок 4 - Функциональная блок-диаграмма процессора ADSP-2192

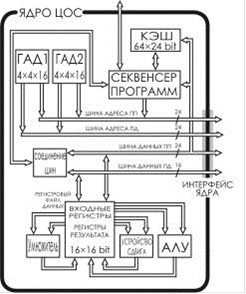

Рисунок 5 - Ядро ЦОС ADSP-219x.

Гибкая архитектура и разноплановая система команд ADSP-2192 поддерживает параллельное выполнение нескольких операций. Например, за один цикл, каждое из ядер ЦОС ADSP-2192 может, помимо стандартных действий ядра ADSP-219х выполнять дополнительные операции.

Эти операции имеют место, пока процессор продолжает:

Получать и/или передавать данные через Хост-порт (PCI или USB интерфейсы)

Получать и/или передавать данные через AC’97

Функциональная блок-диаграмма на рисунке 4 иллюстрирует архитектуру ADSP-2192 процессора с двумя ядрами ЦОС, в то время как блок-диаграмма на рисунке 5 показывает ядро ЦОС семейства ADSP-219x.

Интересное из раздела

Программируемый формирователь последовательности импульсов с цифровой индикацией количества импульсов

Проектируемое устройство в готовом виде представляет собой отдельный прибор, основной функцией которого является формирование последовательности импульсов заданной частот ...

Расчет спектра и энергетических характеристик сигнала

В последнее десятилетие ХХ века произошла научно-техническая революция в

области транспортной связи, в основе которой лежат два крупных достижения науки

сер ...

Организация и расчет сетей поездной и станционной радиосвязи

Бурное развитие радиотехники создало все предпосылки для

широкого использования радиосредств на железнодорожном транспорте. Массовое

внедрение радиосвязи н ...